1.キャッシュメモリとは

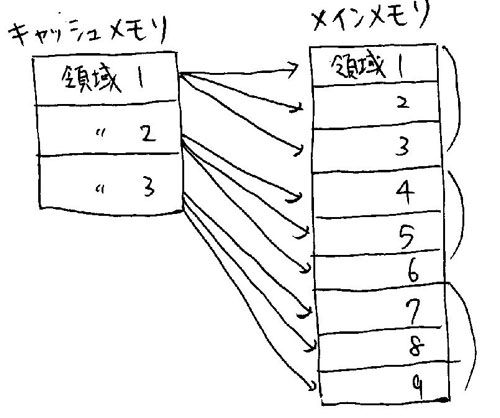

キャッシュメモリに関して過去問(H22春FE午後問1)では、「キャッシュメモリとは,主記憶とCPUの間に置く高速アクセスが可能なメモリである。キャッシュメモリとCPU及び主記憶との関係を図1に示す。データをキャッシュメモリに保持しておくことによって、CPUは速度の遅い主記憶に直接アクセスしなくて済むので,処理の高速化が図れる。」とあります。実際に、過去問(H22春FE午後問1)をみてみましょう。

| 問1 キャッシュメモリに関する次の記述を読んで,設問1, 2に答えよ。 キャッシュメモリとは,主記憶とCPUの間に置く高速アクセスが可能なメモリである。キャッシュメモリとCPU及び主記憶との関係を図1に示す。データをキャッシュメモリに保持しておくことによって、CPUは速度の遅い主記憶に直接アクセスしなくて済むので,処理の高速化が図れる。  ここでは,ハードウェアのアーキテクチャを次のように仮定する。 (1)主記憶はブロック(1ブロックは100語から成る)に分割されている。各ブロックには,その先頭番地が小さいものから順に1, 2, 3,…とブロック番号が振られている。主記憶とキャッシュメモリ間はブロック単位でデータが転送される。 (2)キャッシュメモリには,命令を保持しておく命令キャッシュと,データを保持しておくデータキャッシュの2種類がある。ここでは,データキャッシュ(以下,キャッシュという)だけを考える。 |

Proxyサーバもキャッシュによって高速化する機能があります。

はい。キャッシュメモリもProxyサーバのキャッシュ機能と同様と考えればいいでしょう。

また、キャッシュメモリの効果として,過去問(H28年春FE午前問11)では、「主記憶から読み出したデータをキャッシュメモリに保持し, CPUが後で同じデータを読み出すときのデータ転送を高速に行う。」とあります。

キャッシュメモリは多段構成になっていることが多い。

1次キャッシュ、2次キャッシュと呼ばれる

1次キャッシュは容量が小さいが高速、2次キャッシュは容量が大きいが低速であることが多い。

2次キャッシュにもなければ、メインメモリに問い合わせされる。

過去問(H24年春IP問65)では、CPUのキャッシュメモリに関して、「1次キャッシュは最初にアクセスされ,2次キャッシュは1次キャッシュにデータがないときにアクセスされる。」と述べられています。

また、キャッシュメモリはCPUに内蔵されています。

ですので、PCのスペック一覧では、CPUの欄に記載されています。

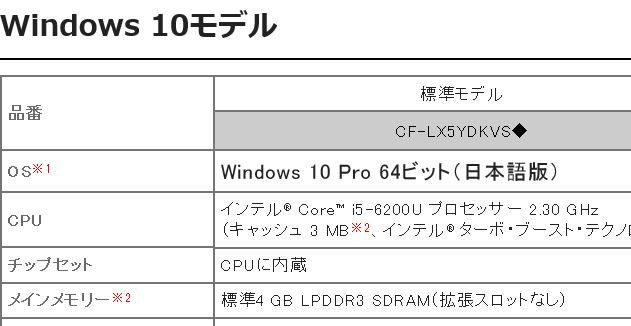

以下はPanasonicのLet's Noteのスペック表です。

https://panasonic.biz/cns/pc/prod/note/lx5y/spec.html

CPUの欄に、キャッシュメモリが3MBであることが記載されています。メインメモリ4GBに比べたら、とても小さいですよね。

参考ですが、自分のPCのキャッシュメモリのサイズを調査するには、CPU-Zなどのツールを入れる必要があります。

このツールを使うと、1次、2次、3次(3次は無い場合場合もあり)毎のメモリ容量が分かります。

2.ヒット率と実効アクセス時間

CPUからのアクセス先は、低速なメモリと高速なキャッシュメモリがあります。キャッシュメモリにデータが存在する(ヒットする)確率をヒット率と言います。また、ヒット率を加味した実効アクセス時間は、以下の式で求められます。

実効アクセス時間=キャッシュメモリのアクセス時間×ヒット率+主記憶のアクセス時間×(1-ヒット率)

応用情報技術者試験では、出題がほとんどありません。

旧い過去問(H21年秋AP午前)までさかのぼると、以下の問題を見つけました。

| 問11 キャッシュメモリのアクセス時間が10ナノ秒,主記憶のアクセス時間が60ナノ秒,キャッシュメモリのヒット率が90%であるときの,実効アクセス時間は何ナノ秒か。 ア 15 イ 25 ウ 35 エ 55 |

↓

↓

↓

↓

【正解】ア

別の過去問(H28春ES午前2問2)を見てみましょう。

| 問2 キャッシュメモリのアクセス時間が主記憶のアクセス時間の1/30で,ヒット率が95%のとき,主記憶の実効アクセス時間は,主記憶のアクセス時間の約何倍になるか。 ア 0.03 イ 0.08 ウ 0.37 エ 0.95 |

↓

↓

↓

↓

【正解】イ

3.メモリデータの対応付け

(1)ダイレクトマップ

過去問(H24春AP午前Ⅱ問10)では、「キャッシュメモリにおけるダイレクトマップ方式」の説明として「一つのメモリブロックをキャッシュ内の単一のロケーションに割り当てる。」と解説しています。キャッシュメモリの領域と、メインメモリのブロックを固定で対応付けます。

メモリブロックって何ですか?

主記憶は一定の大きさでブロックに分割されています。実際の様子は、以下を参照してください。

http://sm.seeeko.com/archives/15876985.html

ダイレクトマップは、以下のようになります。

(2)フルアソシアティブ方式

メインメモリのアドレスと、キャッシュメモリの場所が対応づけされていない方法。つまり、どこに配置してもいいという方法です。特定のダイレクトマップ方式とは対極の関係にあります。(3)セットアソシアティブ方式

ダイレクトマップとフスアソシアティブ方式の折衷案です。一定の領域に区切って、自由に配置(フルアソシアティブ方式)できます。過去問(H21春AP午前問13)を見てみましょう。

| 問13 CPUと主記憶との間に置かれるキャッシュメモリにおいて,主記憶のあるブロックを,キャッシュメモリの複数の特定ブロックに対応付ける方式はどれか。 ア セットアソシアティプ方式 イ ダイレクトマッピング方式 ウ フルアソシアティブ方式 エ ライトスルー方式 |

↓

↓

↓

↓

【正解】ア

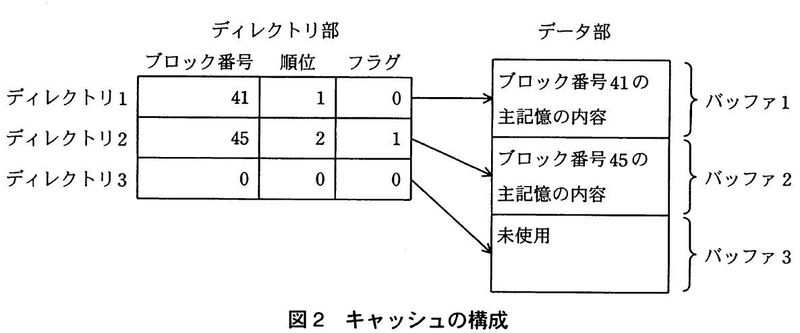

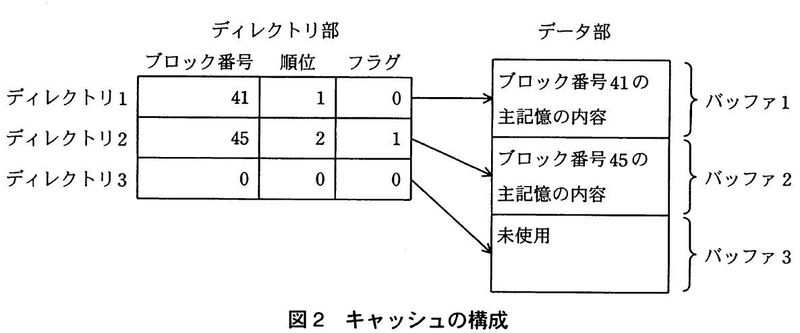

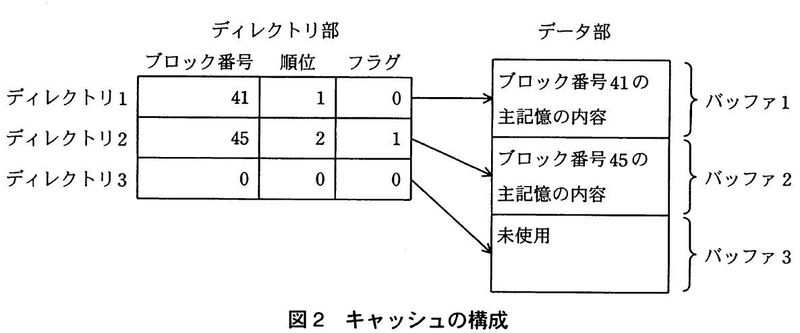

実際の過去問(H22春FE午後問1)を例に、内容の理解を深めましょう。

| (前略) (3)キャッシュの構成は,図2のとおりとする。 ① キャッシュは,ディレクトリ部とデータ部から成る。 ② データ部はバッファ1~3の三つのバッファから成り,各バッファは1ブロック分の主記憶の内容を保持できる。 ③ ディレクトリ部は,データ部のバッファ1~3に対応したディレクトリ1~3から成る。それぞれのディレクトリは次の内容を保持する三つのフィールドから成る。 なお,データ部のバッファが未使用の場合は,対応するディレクトリの三つのフィールドすべてに0が入っている。 (イ)ブロック番号:対応するデータ部のバッファが保持する主記憶のブロック番号 (ロ)順位 :キャッシュ内に最も古くから存在するブロックから順に1, 2, 3と番号が振られる。 (ハ)フラグ:対応するデータ部のバッファにブロックを読み込んだとき, 0に初期化される。対応するデータ部のバッファに保持されている内容がCPUの処理によって変更されると,1に変わる。  |

このときの、キャッシュメモリとメインメモリの領域の割り当ての方法が、上記の3つの方法です。

4.キャッシュメモリのライトスルーとライトバック

過去問(H22春FE午後問1)をみてみましょう。| (2)キャッシュメモリには,命令を保持しておく命令キャッシュと,データを保持しておくデータキャッシュの2種類がある。ここでは,データキャッシュ(以下,キャッシュという)だけを考える。 (3)キャッシュの構成は,図2のとおりとする。 ① キャッシュは,ディレクトリ部とデータ部から成る。 (中略) (ハ)フラグ:対応するデータ部のバッファにブロックを読み込んだとき,0に初期化される。対応するデータ部のバッファに保持されている内容がCPUの処理によって変更されると,1に変わる。  |

じゃあ、キャッシュ(メモリ)だけじゃなく、本当のデータを保存しているメインメモリのデータも変える必要がありますね。

そうなんです。このとき、すぐに書き込むのか後で書き込むのかによって、処理スピードが変わってきます。具体的には、以下で述べる2つの方法があります。

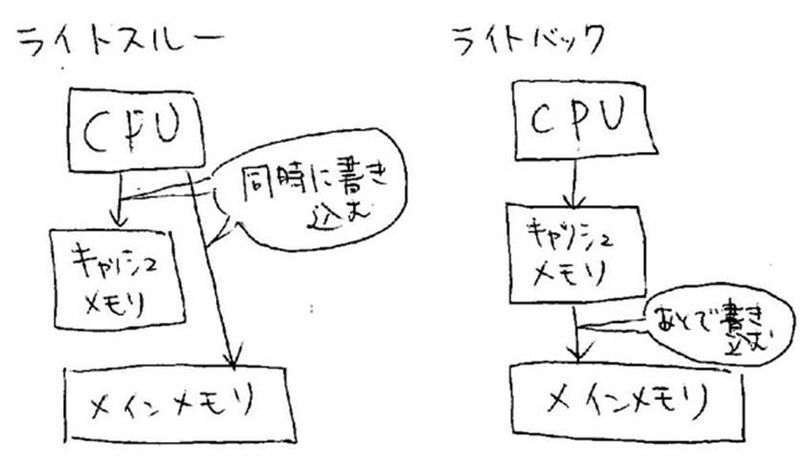

①ライトスルー

過去問(平成29年春期午前問10)では、キャッシュメモリのライトスルーの説明として,「キャッシュメモリと主記憶の両方に同時にデータを書き込む。」と述べています。

②ライトバック

過去問(H24秋SM午前Ⅱ問20)では、「主記憶アクセスの高速化技術であるライトバック方式における,キャッシュメモリ及び主記憶への書込みの説明」として、「キャッシュメモリにだけ書き込み,対応する主記憶の更新は,キャッシュメモリからデータが追い出されるときに行う。」とあります。

過去問(H24秋高度午前Ⅰ問5)を見てみましょう。

| 問5 キャッシュメモリヘの書込み動作には,ライトスルー方式とライトバック方式がある。それぞれの特徴のうち,適切なものはどれか。 ア ライトスルー方式では,データをキャッシュメモリだけに書き込むので,高速に書込みができる。 イ ライトスルー方式では,データをキャッシュメモリと主記憶の両方に同時に書き込むので,主記憶の内容は常に最新である。 ウ ライトバック方式では,データをキャッシュメモリと主記憶の両方に同時に書き込むので,速度が遅い。 エ ライトバック方式では,読出し時にキャッシュミスが発生してキャッシュメモリの内容が追い出されるときに,主記憶に書き戻す必要が生じることはない。 |

↓

↓

↓

↓

↓

【正解】イ

順に見て行きましょう。

ア ライトスルー方式では,データをキャッシュメモリだけに書き込むので,高速に書込みができる。⇒両方に書き込むので、速度が遅くなります。

イ ライトスルー方式では,データをキャッシュメモリと主記憶の両方に同時に書き込むので,主記憶の内容は常に最新である。 ⇒正解

ウ ライトバック方式では,データをキャッシュメモリと主記憶の両方に同時に書き込むので,速度が遅い。⇒後で書き込む、高速です。

エ ライトバック方式では,読出し時にキャッシュミスが発生してキャッシュメモリの内容が追い出されるときに,主記憶に書き戻す必要が生じることはない。 ⇒必要が生じることがあります。

別の過去問(平成29年春期 午前 問10)を見てみましょう。

| 問10 キャッシュメモリのライトスルーの説明として,適切なものはどれか。 ア CPUが書込み動作をする時,キャッシュメモリだけにデータを書き込む。 イ キャッシュメモリと主記憶の両方に同時にデータを書き込む。 ウ 主記憶のデータの変更は,キャッシュメモリから当該データが追い出される時に行う。 エ 主記憶へのアクセス頻度が少ないので,バスの占有率が低い |

↓

↓

↓

↓

↓

【正解】イ

5.参考:割当

過去問(H22春FE午後問1)をみてみましょう。

| (2)キャッシュメモリには,命令を保持しておく命令キャッシュと,データを保持しておくデータキャッシュの2種類がある。ここでは,データキャッシュ(以下,キャッシュという)だけを考える。 (3)キャッシュの構成は,図2のとおりとする。 ① キャッシュは,ディレクトリ部とデータ部から成る。 (中略) (ハ)フラグ:対応するデータ部のバッファにブロックを読み込んだとき,0に初期化される。対応するデータ部のバッファに保持されている内容がCPUの処理によって変更されると,1に変わる。  |

キャッシュにはまず、プログラムなどの命令を保持しておく命令キャッシュと、データを保持しておくデータキャッシュがあります。プログラムなどの命令は、基本的には変わりません。でも、データは演算処理などをすると変わりますよね。

じゃあ、キャッシュ(メモリ)だけじゃなく、本当のデータを保存しているメインメモリのデータも変える必要がありますね。

そうなんです。

6.キャッシュメモリの過去問を解いてみよう

(1)H29春

| 問10 キャッシュメモリのライトスルーの説明として,適切なものはどれか。 ア CPUが書込み動作をする時,キャッシュメモリだけにデータを書き込む。 イ キャッシュメモリと主記憶の両方に同時にデータを書き込む。 ウ 主記憶のデータの変更は,キャッシュメモリから当該データが追い出される時に行う。 エ 主記憶へのアクセス頻度が少ないので,バスの占有率が低い。 |

↓

↓

↓

↓

↓

【正解】イ

(2)H26秋

| 問9 キャッシュの書込み方式には,ライトスルー方式とライトバック方式がある。ライトバック方式を使用する目的として,適切なものはどれか。 ア キャッシュと主記憶の一貫性(コヒーレンシ)を保ちながら,書込みを行う。 イ キャッシュミスが発生したときに,キャッシュの内容の主記憶への書き戻しを不要にする。 ウ 個々のプロセッサがそれぞれのキャッシュをもつマルチプロセッサシステムにおいて,キャッシュ管理をライトスルー方式よりも簡単な回路構成で実現する。 エ プロセッサから主記憶への書込み頻度を減らす。 |

↓

↓

↓

↓

↓

【正解】エ

コメント